# SOFTWARE DESCRIPTION

**Enhanced Generic Test Software Library R&S®EGTSL**

# Software Description for ROHDE & SCHWARZ

### **Enhanced Generic Test Software Library R&S EGTSL**

10th Issue / 08.09 / D 1143.4140.42

This Software Description is valid for the R&S EGTSL-Software version **2.90** and the R&S GTSL-Software version **2.90** (and higher versions).

All rights, also translation into foreign languages, are reserved. No part of this manual is permitted to be reproduced in any form (print, photocopy or any other method), also not for the preparation of lectures, or processed, reproduced or made available using electronic systems without written permission from ROHDE & SCHWARZ.

® The passing on to third parties and the reproduction of this documentation, utilisation and communication of its contents is not permitted unless specifically approved. Infringements will incur claims for damages. All rights reserved in the case of the award of a patent or registration of a design.

$\ensuremath{\mathsf{R\&S}}^\ensuremath{^{\mbox{\it @}}}$  is a registered trademark of ROHDE & SCHWARZ GmbH & Co. KG.

We draw to your attention that the names of software and hardware used in the Software Description, and the brand names of the respective companies are, in general, the subject of protection as trademarks, or under proprietary rights, or patent law.

#### ROHDE & SCHWARZGmbH & Co. KG

Corporate Headquarters

Telephone:

...49 (0)89/4129-13774

Mühldorfstr. 15

Fax:

...49 (0)89/4129-13777

D-81671 München

...49 (0)89/4129-13777

Printed in the Federal Republic of Germany. Errors excepted, subject to technical change without notice.

# **Basic Safety Instructions**

#### Always read through and comply with the following safety instructions!

All plants and locations of the Rohde & Schwarz group of companies make every effort to keep the safety standards of our products up to date and to offer our customers the highest possible degree of safety. Our products and the auxiliary equipment they require are designed, built and tested in accordance with the safety standards that apply in each case. Compliance with these standards is continuously monitored by our quality assurance system. The product described here has been designed, built and tested in accordance with the attached EC Certificate of Conformity and has left the manufacturer's plant in a condition fully complying with safety standards. To maintain this condition and to ensure safe operation, you must observe all instructions and warnings provided in this manual. If you have any questions regarding these safety instructions, the Rohde & Schwarz group of companies will be happy to answer them.

Furthermore, it is your responsibility to use the product in an appropriate manner. This product is designed for use solely in industrial and laboratory environments or, if expressly permitted, also in the field and must not be used in any way that may cause personal injury or property damage. You are responsible if the product is used for any intention other than its designated purpose or in disregard of the manufacturer's instructions. The manufacturer shall assume no responsibility for such use of the product.

The product is used for its designated purpose if it is used in accordance with its product documentation and within its performance limits (see data sheet, documentation, the following safety instructions). Using the product requires technical skills and a basic knowledge of English. It is therefore essential that only skilled and specialized staff or thoroughly trained personnel with the required skills be allowed to use the product. If personal safety gear is required for using Rohde & Schwarz products, this will be indicated at the appropriate place in the product documentation. Keep the basic safety instructions and the product documentation in a safe place and pass them on to the subsequent users.

Observing the safety instructions will help prevent personal injury or damage of any kind caused by dangerous situations. Therefore, carefully read through and adhere to the following safety instructions before and when using the product. It is also absolutely essential to observe the additional safety instructions on personal safety, for example, that appear in relevant parts of the product documentation. In these safety instructions, the word "product" refers to all merchandise sold and distributed by the Rohde & Schwarz group of companies, including instruments, systems and all accessories.

#### Symbols and safety labels

|                                                               | 18 kg                                             | A                              |                         |           |     | 1                             | /-                 |                                                          |

|---------------------------------------------------------------|---------------------------------------------------|--------------------------------|-------------------------|-----------|-----|-------------------------------|--------------------|----------------------------------------------------------|

| Notice, general danger location Observe product documentation | Caution<br>when<br>handling<br>heavy<br>equipment | Danger of<br>electric<br>shock | Warning!<br>Hot surface | PE termi  | nal | Ground                        | Ground<br>terminal | Be careful when handling electrostatic sensitive devices |

| 10                                                            | ()                                                | ===                            | ^                       | <u> </u>  |     | $\sim$                        |                    |                                                          |

| ON/OFF supply voltage                                         | Standby indication                                | Direct current (DC)            | Alternating (AC)        | g current |     | ct/alternating<br>ent (DC/AC) |                    | y protected by<br>inforced) insulation                   |

#### Tags and their meaning

The following signal words are used in the product documentation in order to warn the reader about risks and dangers.

indicates a hazardous situation which, if not avoided, will result in death or serious injury.

indicates a hazardous situation which, if not avoided, could result in death or serious injury.

indicates a hazardous situation which, if not avoided, could result in minor or moderate injury.

indicates the possibility of incorrect operation which can result in damage to the product.

In the product documentation, the word ATTENTION is used synonymously.

These tags are in accordance with the standard definition for civil applications in the European Economic Area. Definitions that deviate from the standard definition may also exist in other economic areas or military applications. It is therefore essential to make sure that the tags described here are always used only in connection with the related product documentation and the related product. The use of tags in connection with unrelated products or documentation can result in misinterpretation and in personal injury or material damage.

#### Operating states and operating positions

The product may be operated only under the operating conditions and in the positions specified by the manufacturer, without the product's ventilation being obstructed. If the manufacturer's specifications are not observed, this can result in electric shock, fire and/or serious personal injury or death. Applicable local or national safety regulations and rules for the prevention of accidents must be observed in all work performed.

- Unless otherwise specified, the following requirements apply to Rohde & Schwarz products: predefined operating position is always with the housing floor facing down, IP protection 2X, pollution severity 2, overvoltage category 2, use only indoors, max. operating altitude 2000 m above sea level, max. transport altitude 4500 m above sea level. A tolerance of ±10 % shall apply to the nominal voltage and ±5 % to the nominal frequency.

- 2. Do not place the product on surfaces, vehicles, cabinets or tables that for reasons of weight or stability are unsuitable for this purpose. Always follow the manufacturer's installation instructions when installing the product and fastening it to objects or structures (e.g. walls and shelves). An installation that is not carried out as described in the product documentation could result in personal injury or death.

- Do not place the product on heat-generating devices such as radiators or fan heaters. The ambient temperature must not exceed the maximum temperature specified in the product documentation or in the data sheet. Product overheating can cause electric shock, fire and/or serious personal injury or death.

#### **Electrical safety**

If the information on electrical safety is not observed either at all to the extent necessary, electric shock, fire and/or serious personal injury or death may occur.

- 1. Prior to switching on the product, always ensure that the nominal voltage setting on the product matches the nominal voltage of the AC supply network. If a different voltage is to be set, the power fuse of the product may have to be changed accordingly.

- 2. In the case of products of safety class I with movable power cord and connector, operation is permitted only on sockets with an earthing contact and protective earth connection.

- 3. Intentionally breaking the protective earth connection either in the feed line or in the product itself is not permitted. Doing so can result in the danger of an electric shock from the product. If extension cords or connector strips are implemented, they must be checked on a regular basis to ensure that they are safe to use.

- 4. If the product does not have a power switch for disconnection from the AC supply network, the plug of the connecting cable is regarded as the disconnecting device. In such cases, always ensure that the power plug is easily reachable and accessible at all times (corresponding to the length of connecting cable, approx. 2 m). Functional or electronic switches are not suitable for providing disconnection from the AC supply network. If products without power switches are integrated into racks or systems, a disconnecting device must be provided at the system level.

- 5. Never use the product if the power cable is damaged. Check the power cable on a regular basis to ensure that it is in proper operating condition. By taking appropriate safety measures and carefully laying the power cable, you can ensure that the cable will not be damaged and that no one can be hurt by, for example, tripping over the cable or suffering an electric shock.

- 6. The product may be operated only from TN/TT supply networks fused with max. 16 A (higher fuse only after consulting with the Rohde & Schwarz group of companies).

- 7. Do not insert the plug into sockets that are dusty or dirty. Insert the plug firmly and all the way into the socket. Otherwise, sparks that result in fire and/or injuries may occur.

- 8. Do not overload any sockets, extension cords or connector strips; doing so can cause fire or electric shocks.

- 9. For measurements in circuits with voltages V<sub>rms</sub> > 30 V, suitable measures (e.g. appropriate measuring equipment, fusing, current limiting, electrical separation, insulation) should be taken to avoid any hazards.

- 10. Ensure that the connections with information technology equipment, e.g. PCs or other industrial computers, comply with the IEC60950-1/EN60950-1 or IEC61010-1/EN 61010-1 standards that apply in each case.

- 11. Unless expressly permitted, never remove the cover or any part of the housing while the product is in operation. Doing so will expose circuits and components and can lead to injuries, fire or damage to the product.

- 12. If a product is to be permanently installed, the connection between the PE terminal on site and the product's PE conductor must be made first before any other connection is made. The product may be installed and connected only by a licensed electrician.

- 13. For permanently installed equipment without built-in fuses, circuit breakers or similar protective devices, the supply circuit must be fused in such a way that anyone who has access to the product, as well as the product itself, is adequately protected from injury or damage.

- 14. Use suitable overvoltage protection to ensure that no overvoltage (such as that caused by a bolt of lightning) can reach the product. Otherwise, the person operating the product will be exposed to the danger of an electric shock.

- 15. Any object that is not designed to be placed in the openings of the housing must not be used for this purpose. Doing so can cause short circuits inside the product and/or electric shocks, fire or injuries.

- 16. Unless specified otherwise, products are not liquid-proof (see also section "Operating states and operating positions", item 1. Therefore, the equipment must be protected against penetration by liquids. If the necessary precautions are not taken, the user may suffer electric shock or the product itself may be damaged, which can also lead to personal injury.

- 17. Never use the product under conditions in which condensation has formed or can form in or on the product, e.g. if the product has been moved from a cold to a warm environment. Penetration by water increases the risk of electric shock.

- 18. Prior to cleaning the product, disconnect it completely from the power supply (e.g. AC supply network or battery). Use a soft, non-linting cloth to clean the product. Never use chemical cleaning agents such as alcohol, acetone or diluents for cellulose lacquers.

#### Operation

- Operating the products requires special training and intense concentration. Make sure that persons

who use the products are physically, mentally and emotionally fit enough to do so; otherwise, injuries

or material damage may occur. It is the responsibility of the employer/operator to select suitable

personnel for operating the products.

- 2. Before you move or transport the product, read and observe the section titled "Transport".

- 3. As with all industrially manufactured goods, the use of substances that induce an allergic reaction (allergens) such as nickel cannot be generally excluded. If you develop an allergic reaction (such as a skin rash, frequent sneezing, red eyes or respiratory difficulties) when using a Rohde & Schwarz product, consult a physician immediately to determine the cause and to prevent health problems or stress.

- 4. Before you start processing the product mechanically and/or thermally, or before you take it apart, be sure to read and pay special attention to the section titled "Waste disposal", item 1.

- 5. Depending on the function, certain products such as RF radio equipment can produce an elevated level of electromagnetic radiation. Considering that unborn babies require increased protection, pregnant women must be protected by appropriate measures. Persons with pacemakers may also be exposed to risks from electromagnetic radiation. The employer/operator must evaluate workplaces where there is a special risk of exposure to radiation and, if necessary, take measures to avert the potential danger.

- 6. Should a fire occur, the product may release hazardous substances (gases, fluids, etc.) that can cause health problems. Therefore, suitable measures must be taken, e.g. protective masks and protective clothing must be worn.

- 7. If a laser product (e.g. a CD/DVD drive) is integrated into a Rohde & Schwarz product, absolutely no other settings or functions may be used as described in the product documentation. The objective is to prevent personal injury (e.g. due to laser beams).

#### Repair and service

- 1. The product may be opened only by authorized, specially trained personnel. Before any work is performed on the product or before the product is opened, it must be disconnected from the AC supply network. Otherwise, personnel will be exposed to the risk of an electric shock.

- 2. Adjustments, replacement of parts, maintenance and repair may be performed only by electrical experts authorized by Rohde & Schwarz. Only original parts may be used for replacing parts relevant to safety (e.g. power switches, power transformers, fuses). A safety test must always be performed after parts relevant to safety have been replaced (visual inspection, PE conductor test, insulation resistance measurement, leakage current measurement, functional test). This helps ensure the continued safety of the product.

#### Batteries and rechargeable batteries/cells

If the information regarding batteries and rechargeable batteries/cells is not observed either at all or to the extent necessary, product users may be exposed to the risk of explosions, fire and/or serious personal injury, and, in some cases, death. Batteries and rechargeable batteries with alkaline electrolytes (e.g. lithium cells) must be handled in accordance with the EN 62133 standard.

- 1. Cells must not be taken apart or crushed.

- 2. Cells or batteries must not be exposed to heat or fire. Storage in direct sunlight must be avoided. Keep cells and batteries clean and dry. Clean soiled connectors using a dry, clean cloth.

- 3. Cells or batteries must not be short-circuited. Cells or batteries must not be stored in a box or in a drawer where they can short-circuit each other, or where they can be short-circuited by other conductive materials. Cells and batteries must not be removed from their original packaging until they are ready to be used.

- 4. Keep cells and batteries out of the hands of children. If a cell or a battery has been swallowed, seek medical aid immediately.

- 5. Cells and batteries must not be exposed to any mechanical shocks that are stronger than permitted.

- 6. If a cell develops a leak, the fluid must not be allowed to come into contact with the skin or eyes. If contact occurs, wash the affected area with plenty of water and seek medical aid.

- 7. Improperly replacing or charging cells or batteries that contain alkaline electrolytes (e.g. lithium cells) can cause explosions. Replace cells or batteries only with the matching Rohde & Schwarz type (see parts list) in order to ensure the safety of the product.

- 8. Cells and batteries must be recycled and kept separate from residual waste. Rechargeable batteries and normal batteries that contain lead, mercury or cadmium are hazardous waste. Observe the national regulations regarding waste disposal and recycling.

#### **Transport**

The product may be very heavy. Therefore, the product must be handled with care. In some cases, the user may require a suitable means of lifting or moving the product (e.g. with a lift-truck) to avoid back or other physical injuries.

- 2. Handles on the products are designed exclusively to enable personnel to transport the product. It is therefore not permissible to use handles to fasten the product to or on transport equipment such as cranes, fork lifts, wagons, etc. The user is responsible for securely fastening the products to or on the means of transport or lifting. Observe the safety regulations of the manufacturer of the means of transport or lifting. Noncompliance can result in personal injury or material damage.

- 3. If you use the product in a vehicle, it is the sole responsibility of the driver to drive the vehicle safely and properly. The manufacturer assumes no responsibility for accidents or collisions. Never use the product in a moving vehicle if doing so could distract the driver of the vehicle. Adequately secure the product in the vehicle to prevent injuries or other damage in the event of an accident.

#### Waste disposal

- If products or their components are mechanically and/or thermally processed in a manner that goes beyond their intended use, hazardous substances (heavy-metal dust such as lead, beryllium, nickel) may be released. For this reason, the product may only be disassembled by specially trained personnel. Improper disassembly may be hazardous to your health. National waste disposal regulations must be observed.

- 2. If handling the product releases hazardous substances or fuels that must be disposed of in a special way, e.g. coolants or engine oils that must be replenished regularly, the safety instructions of the manufacturer of the hazardous substances or fuels and the applicable regional waste disposal regulations must be observed. Also observe the relevant safety instructions in the product documentation. The improper disposal of hazardous substances or fuels can cause health problems and lead to environmental damage.

# Informaciones elementales de seguridad

#### Es imprescindible leer y observar las siguientes instrucciones e informaciones de seguridad!

El principio del grupo de empresas Rohde & Schwarz consiste en tener nuestros productos siempre al día con los estándares de seguridad y de ofrecer a nuestros clientes el máximo grado de seguridad. Nuestros productos y todos los equipos adicionales son siempre fabricados y examinados según las normas de seguridad vigentes. Nuestro sistema de garantía de calidad controla constantemente que sean cumplidas estas normas. El presente producto ha sido fabricado y examinado según el certificado de conformidad adjunto de la UE y ha salido de nuestra planta en estado impecable según los estándares técnicos de seguridad. Para poder preservar este estado y garantizar un funcionamiento libre de peligros, el usuario deberá atenerse a todas las indicaciones, informaciones de seguridad y notas de alerta. El grupo de empresas Rohde & Schwarz está siempre a su disposición en caso de que tengan preguntas referentes a estas informaciones de seguridad.

Además queda en la responsabilidad del usuario utilizar el producto en la forma debida. Este producto está destinado exclusivamente al uso en la industria y el laboratorio o, si ha sido expresamente autorizado, para aplicaciones de campo y de ninguna manera deberá ser utilizado de modo que alguna persona/cosa pueda sufrir daño. El uso del producto fuera de sus fines definidos o sin tener en cuenta las instrucciones del fabricante queda en la responsabilidad del usuario. El fabricante no se hace en ninguna forma responsable de consecuencias a causa del mal uso del producto.

Se parte del uso correcto del producto para los fines definidos si el producto es utilizado conforme a las indicaciones de la correspondiente documentación del producto y dentro del margen de rendimiento definido (ver hoja de datos, documentación, informaciones de seguridad que siguen). El uso del producto hace necesarios conocimientos técnicos y ciertos conocimientos del idioma inglés. Por eso se debe tener en cuenta que el producto solo pueda ser operado por personal especializado o personas instruidas en profundidad con las capacidades correspondientes. Si fuera necesaria indumentaria de seguridad para el uso de productos de Rohde & Schwarz, encontraría la información debida en la documentación del producto en el capítulo correspondiente. Guarde bien las informaciones de seguridad elementales, así como la documentación del producto, y entréguelas a usuarios posteriores.

Tener en cuenta las informaciones de seguridad sirve para evitar en lo posible lesiones o daños por peligros de toda clase. Por eso es imprescindible leer detalladamente y comprender por completo las siguientes informaciones de seguridad antes de usar el producto, y respetarlas durante el uso del producto. Deberán tenerse en cuenta todas las demás informaciones de seguridad, como p. ej. las referentes a la protección de personas, que encontrarán en el capítulo correspondiente de la documentación del producto y que también son de obligado cumplimiento. En las presentes informaciones de seguridad se recogen todos los objetos que distribuye el grupo de empresas Rohde & Schwarz bajo la denominación de "producto", entre ellos también aparatos, instalaciones así como toda clase de accesorios.

#### Símbolos y definiciones de seguridad

|                                                                                    | 18 kg                                                             | 4                                 |                                             |                                    | =                    | <i>/</i>           |                                                                                                |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|---------------------------------------------|------------------------------------|----------------------|--------------------|------------------------------------------------------------------------------------------------|

| Aviso: punto de<br>peligro general<br>Observar la<br>documentación<br>del producto | Atención en<br>el manejo de<br>dispositivos<br>de peso<br>elevado | Peligro de<br>choque<br>eléctrico | Adver-<br>tencia:<br>superficie<br>caliente | Conexión a conductor de protección | Conexión<br>a tierra | Conexión<br>a masa | Aviso: Cuidado<br>en el manejo de<br>dispositivos<br>sensibles a la<br>electrostática<br>(ESD) |

| 10                                                               | (1)                                               |                         | ~                      | ~                                              |                                                                                         |

|------------------------------------------------------------------|---------------------------------------------------|-------------------------|------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|

| Tensión de<br>alimentación de<br>PUESTA EN<br>MARCHA /<br>PARADA | Indicación de<br>estado de<br>espera<br>(Standby) | Corriente continua (DC) | Corriente alterna (AC) | Corriente continua / Corriente alterna (DC/AC) | El aparato está protegido<br>en su totalidad por un<br>aislamiento doble<br>(reforzado) |

#### Palabras de señal y su significado

En la documentación del producto se utilizan las siguientes palabras de señal con el fin de advertir contra riesgos y peligros.

PELIGRO identifica un peligro inminente con riesgo elevado que provocará muerte o lesiones graves si no se evita.

ADVERTENCIA identifica un posible peligro con riesgo medio de provocar muerte o lesiones (graves) si no se evita.

ATENCIÓN identifica un peligro con riesgo reducido de provocar lesiones leves o moderadas si no se evita.

AVISO indica la posibilidad de utilizar mal el producto y, como consecuencia, dañarlo.

En la documentación del producto se emplea de forma sinónima el término CUIDADO.

Las palabras de señal corresponden a la definición habitual para aplicaciones civiles en el área económica europea. Pueden existir definiciones diferentes a esta definición en otras áreas económicas o en aplicaciones militares. Por eso se deberá tener en cuenta que las palabras de señal aquí descritas sean utilizadas siempre solamente en combinación con la correspondiente documentación del producto y solamente en combinación con el producto correspondiente. La utilización de las palabras de señal en combinación con productos o documentaciones que no les correspondan puede llevar a interpretaciones equivocadas y tener por consecuencia daños en personas u objetos.

#### Estados operativos y posiciones de funcionamiento

El producto solamente debe ser utilizado según lo indicado por el fabricante respecto a los estados operativos y posiciones de funcionamiento sin que se obstruya la ventilación. Si no se siguen las indicaciones del fabricante, pueden producirse choques eléctricos, incendios y/o lesiones graves con posible consecuencia de muerte. En todos los trabajos deberán ser tenidas en cuenta las normas nacionales y locales de seguridad del trabajo y de prevención de accidentes.

- 1. Si no se convino de otra manera, es para los productos Rohde & Schwarz válido lo que sigue: como posición de funcionamiento se define por principio la posición con el suelo de la caja para abajo, modo de protección IP 2X, grado de suciedad 2, categoría de sobrecarga eléctrica 2, uso solamente en estancias interiores, utilización hasta 2000 m sobre el nivel del mar, transporte hasta 4500 m sobre el nivel del mar. Se aplicará una tolerancia de ±10 % sobre el voltaje nominal y de ±5 % sobre la frecuencia nominal.

- 2. No sitúe el producto encima de superficies, vehículos, estantes o mesas, que por sus características de peso o de estabilidad no sean aptos para él. Siga siempre las instrucciones de instalación del fabricante cuando instale y asegure el producto en objetos o estructuras (p. ej. paredes y estantes). Si se realiza la instalación de modo distinto al indicado en la documentación del producto, pueden causarse lesiones o incluso la muerte.

- 3. No ponga el producto sobre aparatos que generen calor (p. ej. radiadores o calefactores). La temperatura ambiente no debe superar la temperatura máxima especificada en la documentación del producto o en la hoja de datos. En caso de sobrecalentamiento del producto, pueden producirse choques eléctricos, incendios y/o lesiones graves con posible consecuencia de muerte.

#### Seguridad eléctrica

Si no se siguen (o se siguen de modo insuficiente) las indicaciones del fabricante en cuanto a seguridad eléctrica, pueden producirse choques eléctricos, incendios y/o lesiones graves con posible consecuencia de muerte.

- Antes de la puesta en marcha del producto se deberá comprobar siempre que la tensión preseleccionada en el producto coincida con la de la red de alimentación eléctrica. Si es necesario modificar el ajuste de tensión, también se deberán cambiar en caso dado los fusibles correspondientes del producto.

- 2. Los productos de la clase de protección I con alimentación móvil y enchufe individual solamente podrán enchufarse a tomas de corriente con contacto de seguridad y con conductor de protección conectado.

- 3. Queda prohibida la interrupción intencionada del conductor de protección, tanto en la toma de corriente como en el mismo producto. La interrupción puede tener como consecuencia el riesgo de que el producto sea fuente de choques eléctricos. Si se utilizan cables alargadores o regletas de enchufe, deberá garantizarse la realización de un examen regular de los mismos en cuanto a su estado técnico de seguridad.

- 4. Si el producto no está equipado con un interruptor para desconectarlo de la red, se deberá considerar el enchufe del cable de conexión como interruptor. En estos casos se deberá asegurar que el enchufe siempre sea de fácil acceso (de acuerdo con la longitud del cable de conexión, aproximadamente 2 m). Los interruptores de función o electrónicos no son aptos para el corte de la red eléctrica. Si los productos sin interruptor están integrados en bastidores o instalaciones, se deberá colocar el interruptor en el nivel de la instalación.

- 5. No utilice nunca el producto si está dañado el cable de conexión a red. Compruebe regularmente el correcto estado de los cables de conexión a red. Asegúrese, mediante las medidas de protección y de instalación adecuadas, de que el cable de conexión a red no pueda ser dañado o de que nadie pueda ser dañado por él, p. ej. al tropezar o por un choque eléctrico.

- Solamente está permitido el funcionamiento en redes de alimentación TN/TT aseguradas con fusibles de 16 A como máximo (utilización de fusibles de mayor amperaje solo previa consulta con el grupo de empresas Rohde & Schwarz).

- 7. Nunca conecte el enchufe en tomas de corriente sucias o llenas de polvo. Introduzca el enchufe por completo y fuertemente en la toma de corriente. La no observación de estas medidas puede provocar chispas, fuego y/o lesiones.

- 8. No sobrecargue las tomas de corriente, los cables alargadores o las regletas de enchufe ya que esto podría causar fuego o choques eléctricos.

- En las mediciones en circuitos de corriente con una tensión U<sub>eff</sub> > 30 V se deberán tomar las medidas apropiadas para impedir cualquier peligro (p. ej. medios de medición adecuados, seguros, limitación de tensión, corte protector, aislamiento etc.).

- Para la conexión con dispositivos informáticos como un PC o un ordenador industrial, debe comprobarse que éstos cumplan los estándares IEC60950-1/EN60950-1 o IEC61010-1/EN 61010-1 válidos en cada caso.

- 11. A menos que esté permitido expresamente, no retire nunca la tapa ni componentes de la carcasa mientras el producto esté en servicio. Esto pone a descubierto los cables y componentes eléctricos y puede causar lesiones, fuego o daños en el producto.

- 12. Si un producto se instala en un lugar fijo, se deberá primero conectar el conductor de protección fijo con el conductor de protección del producto antes de hacer cualquier otra conexión. La instalación y la conexión deberán ser efectuadas por un electricista especializado.

- 13. En el caso de dispositivos fijos que no estén provistos de fusibles, interruptor automático ni otros mecanismos de seguridad similares, el circuito de alimentación debe estar protegido de modo que todas las personas que puedan acceder al producto, así como el producto mismo, estén a salvo de posibles daños.

- 14. Todo producto debe estar protegido contra sobretensión (debida p. ej. a una caída del rayo) mediante los correspondientes sistemas de protección. Si no, el personal que lo utilice quedará expuesto al peligro de choque eléctrico.

- 15. No debe introducirse en los orificios de la caja del aparato ningún objeto que no esté destinado a ello. Esto puede producir cortocircuitos en el producto y/o puede causar choques eléctricos, fuego o lesiones.

- 16. Salvo indicación contraria, los productos no están impermeabilizados (ver también el capítulo "Estados operativos y posiciones de funcionamiento", punto 1). Por eso es necesario tomar las medidas necesarias para evitar la entrada de líquidos. En caso contrario, existe peligro de choque eléctrico para el usuario o de daños en el producto, que también pueden redundar en peligro para las personas.

- 17. No utilice el producto en condiciones en las que pueda producirse o ya se hayan producido condensaciones sobre el producto o en el interior de éste, como p. ej. al desplazarlo de un lugar frío a otro caliente. La entrada de agua aumenta el riesgo de choque eléctrico.

- 18. Antes de la limpieza, desconecte por completo el producto de la alimentación de tensión (p. ej. red de alimentación o batería). Realice la limpieza de los aparatos con un paño suave, que no se deshilache. No utilice bajo ningún concepto productos de limpieza químicos como alcohol, acetona o diluyentes para lacas nitrocelulósicas.

#### **Funcionamiento**

- 1. El uso del producto requiere instrucciones especiales y una alta concentración durante el manejo. Debe asegurarse que las personas que manejen el producto estén a la altura de los requerimientos necesarios en cuanto a aptitudes físicas, psíquicas y emocionales, ya que de otra manera no se pueden excluir lesiones o daños de objetos. El empresario u operador es responsable de seleccionar el personal usuario apto para el manejo del producto.

- 2. Antes de desplazar o transportar el producto, lea y tenga en cuenta el capítulo "Transporte".

- 3. Como con todo producto de fabricación industrial no puede quedar excluida en general la posibilidad de que se produzcan alergias provocadas por algunos materiales empleados, los llamados alérgenos (p. ej. el níquel). Si durante el manejo de productos Rohde & Schwarz se producen reacciones alérgicas, como p. ej. irritaciones cutáneas, estornudos continuos, enrojecimiento de la conjuntiva o dificultades respiratorias, debe avisarse inmediatamente a un médico para investigar las causas y evitar cualquier molestia o daño a la salud.

- 4. Antes de la manipulación mecánica y/o térmica o el desmontaje del producto, debe tenerse en cuenta imprescindiblemente el capítulo "Eliminación", punto 1.

- 5. Ciertos productos, como p. ej. las instalaciones de radiocomunicación RF, pueden a causa de su función natural, emitir una radiación electromagnética aumentada. Deben tomarse todas las medidas necesarias para la protección de las mujeres embarazadas. También las personas con marcapasos pueden correr peligro a causa de la radiación electromagnética. El empresario/operador tiene la obligación de evaluar y señalizar las áreas de trabajo en las que exista un riesgo elevado de exposición a radiaciones.

- 6. Tenga en cuenta que en caso de incendio pueden desprenderse del producto sustancias tóxicas (gases, líquidos etc.) que pueden generar daños a la salud. Por eso, en caso de incendio deben usarse medidas adecuadas, como p. ej. máscaras antigás e indumentaria de protección.

- 7. En caso de que un producto Rohde & Schwarz contenga un producto láser (p. ej. un lector de CD/DVD), no debe usarse ninguna otra configuración o función aparte de las descritas en la documentación del producto, a fin de evitar lesiones (p. ej. debidas a irradiación láser).

#### Reparación y mantenimiento

- 1. El producto solamente debe ser abierto por personal especializado con autorización para ello. Antes de manipular el producto o abrirlo, es obligatorio desconectarlo de la tensión de alimentación, para evitar toda posibilidad de choque eléctrico.

- 2. El ajuste, el cambio de partes, el mantenimiento y la reparación deberán ser efectuadas solamente por electricistas autorizados por Rohde & Schwarz. Si se reponen partes con importancia para los aspectos de seguridad (p. ej. el enchufe, los transformadores o los fusibles), solamente podrán ser sustituidos por partes originales. Después de cada cambio de partes relevantes para la seguridad deberá realizarse un control de seguridad (control a primera vista, control del conductor de protección, medición de resistencia de aislamiento, medición de la corriente de fuga, control de funcionamiento). Con esto queda garantizada la seguridad del producto.

#### Baterías y acumuladores o celdas

Si no se siguen (o se siguen de modo insuficiente) las indicaciones en cuanto a las baterías y acumuladores o celdas, pueden producirse explosiones, incendios y/o lesiones graves con posible consecuencia de muerte. El manejo de baterías y acumuladores con electrolitos alcalinos (p. ej. celdas de litio) debe seguir el estándar EN 62133.

- 1. No deben desmontarse, abrirse ni triturarse las celdas.

- 2. Las celdas o baterías no deben someterse a calor ni fuego. Debe evitarse el almacenamiento a la luz directa del sol. Las celdas y baterías deben mantenerse limpias y secas. Limpiar las conexiones sucias con un paño seco y limpio.

- 3. Las celdas o baterías no deben cortocircuitarse. Es peligroso almacenar las celdas o baterías en estuches o cajones en cuyo interior puedan cortocircuitarse por contacto recíproco o por contacto con otros materiales conductores. No deben extraerse las celdas o baterías de sus embalajes originales hasta el momento en que vayan a utilizarse.

- 4. Mantener baterías y celdas fuera del alcance de los niños. En caso de ingestión de una celda o batería, avisar inmediatamente a un médico.

- 5. Las celdas o baterías no deben someterse a impactos mecánicos fuertes indebidos.

- 6. En caso de falta de estanqueidad de una celda, el líquido vertido no debe entrar en contacto con la piel ni los ojos. Si se produce contacto, lavar con agua abundante la zona afectada y avisar a un médico.

- 7. En caso de cambio o recarga inadecuados, las celdas o baterías que contienen electrolitos alcalinos (p. ej. las celdas de litio) pueden explotar. Para garantizar la seguridad del producto, las celdas o baterías solo deben ser sustituidas por el tipo Rohde & Schwarz correspondiente (ver lista de recambios).

- 8. Las baterías y celdas deben reciclarse y no deben tirarse a la basura doméstica. Las baterías o acumuladores que contienen plomo, mercurio o cadmio deben tratarse como residuos especiales. Respete en esta relación las normas nacionales de eliminación y reciclaje.

#### **Transporte**

- 1. El producto puede tener un peso elevado. Por eso es necesario desplazarlo o transportarlo con precaución y, si es necesario, usando un sistema de elevación adecuado (p. ej. una carretilla elevadora), a fin de evitar lesiones en la espalda u otros daños personales.

- 2. Las asas instaladas en los productos sirven solamente de ayuda para el transporte del producto por personas. Por eso no está permitido utilizar las asas para la sujeción en o sobre medios de transporte como p. ej. grúas, carretillas elevadoras de horquilla, carros etc. Es responsabilidad suya fijar los productos de manera segura a los medios de transporte o elevación. Para evitar daños personales o daños en el producto, siga las instrucciones de seguridad del fabricante del medio de transporte o elevación utilizado.

- 3. Si se utiliza el producto dentro de un vehículo, recae de manera exclusiva en el conductor la responsabilidad de conducir el vehículo de manera segura y adecuada. El fabricante no asumirá ninguna responsabilidad por accidentes o colisiones. No utilice nunca el producto dentro de un vehículo en movimiento si esto pudiera distraer al conductor. Asegure el producto dentro del vehículo debidamente para evitar, en caso de un accidente, lesiones u otra clase de daños.

#### Eliminación

- 1. Si se trabaja de manera mecánica y/o térmica cualquier producto o componente más allá del funcionamiento previsto, pueden liberarse sustancias peligrosas (polvos con contenido de metales pesados como p. ej. plomo, berilio o níquel). Por eso el producto solo debe ser desmontado por personal especializado con formación adecuada. Un desmontaje inadecuado puede ocasionar daños para la salud. Se deben tener en cuenta las directivas nacionales referentes a la eliminación de residuos.

- 2. En caso de que durante el trato del producto se formen sustancias peligrosas o combustibles que deban tratarse como residuos especiales (p. ej. refrigerantes o aceites de motor con intervalos de cambio definidos), deben tenerse en cuenta las indicaciones de seguridad del fabricante de dichas sustancias y las normas regionales de eliminación de residuos. Tenga en cuenta también en caso necesario las indicaciones de seguridad especiales contenidas en la documentación del producto. La eliminación incorrecta de sustancias peligrosas o combustibles puede causar daños a la salud o daños al medio ambiente.

# **Certified Quality System**

DIN EN ISO 9001 : 2000 DIN EN 9100 : 2003 DIN EN ISO 14001 : 2004

DQS REG. NO 001954 QM UM

### **QUALITÄTSZERTIFIKAT**

Sehr geehrter Kunde,

Sie haben sich für den Kauf eines

Rohde & Schwarz-Produktes entschieden. Hiermit erhalten Sie ein

nach modernsten Fertigungsmethoden hergestelltes Produkt. Es

wurde nach den Regeln unseres

Managementsystems entwickelt,

gefertigt und geprüft.

Das Rohde & Schwarz Managementsystem ist zertifiziert nach:

DIN EN ISO 9001:2000 DIN EN 9100:2003 DIN EN ISO 14001:2004

#### **CERTIFICATE OF QUALITY**

Dear Customer.

you have decided to buy a Rohde & Schwarz product. You are thus assured of receiving a product that is manufactured using the most modern methods available. This product was developed, manufactured and tested in compliance with our quality management system standards. The Rohde & Schwarz quality

The Rohde & Schwarz quality management system is certified according to:

DIN EN ISO 9001:2000 DIN EN 9100:2003 DIN EN ISO 14001:2004

#### CERTIFICAT DE QUALITÉ

Cher Client,

vous avez choisi d'acheter un produit Rohde & Schwarz. Vous disposez donc d'un produit fabriqué d'après les méthodes les plus avancées. Le développement, la fabrication et les tests respectent nos normes de gestion qualité.

Le système de gestion qualité de Rohde & Schwarz a été homologué conformément aux normes:

DIN EN ISO 9001:2000 DIN EN 9100:2003 DIN EN ISO 14001:2004

#### **Address List**

#### Headquarters, Plants and Subsidiaries

#### Headquarters

ROHDE&SCHWARZ GmbH & Co. KG Mühldorfstraße 15 · D-81671 München P.O.Box 80 14 69 · D-81614 München Phone +49 (89) 41 29-0 Fax +49 (89) 41 29-121 64 info.rs@rohde-schwarz.com

#### **Plants**

ROHDE&SCHWARZ Messgerätebau GmbH Riedbachstraße 58 · D-87700 Memmingen P.O.Box 16 52 · D-87686 Memmingen

ROHDE&SCHWARZ GmbH & Co. KG Werk Teisnach Kaikenrieder Straße 27 · D-94244 Teisnach P.O.Box 11 49 · D-94240 Teisnach

ROHDE&SCHWARZ závod Vimperk, s.r.o. Location Spidrova 49 CZ-38501 Vimperk

ROHDE&SCHWARZ GmbH & Co. KG Dienstleistungszentrum Köln Graf-Zeppelin-Straße 18 · D-51147 Köln P.O.Box 98 02 60 · D-51130 Köln

#### **Subsidiaries**

R&S BICK Mobilfunk GmbH Fritz-Hahne-Str. 7 · D-31848 Bad Münder P.O.Box 20 02 · D-31844 Bad Münder

ROHDE&SCHWARZ FTK GmbH Wendenschloßstraße 168, Haus 28 D-12557 Berlin

ROHDE&SCHWARZ SIT GmbH Am Studio 3 D-12489 Berlin

R&S Systems GmbH Graf-Zeppelin-Straße 18 D-51147 Köln

GEDIS GmbH Sophienblatt 100 D-24114 Kiel

HAMEG Instruments GmbH Industriestraße 6 D-63533 Mainhausen Phone +49 (83 31) 1 08-0 +49 (83 31) 1 08-1124

Phone +49 (99 23) 8 50-0 Fax +49 (99 23) 8 50-174 info.rsdts@rohde-schwarz.com

> Phone +420 (388) 45 21 09 Fax +420 (388) 45 21 13

Phone +49 (22 03) 49-0 Fax +49 (22 03) 49 51-229 info.rsdc@rohde-schwarz.com service.rsdc@rohde-schwarz.com

> Phone +49 (50 42) 9 98-0 Fax +49 (50 42) 9 98-105

> Phone +49 (30) 658 91-122 Fax +49 (30) 655 50-221 info.ftk@rohde-schwarz.com

Phone +49 (30) 658 84-0 Fax +49 (30) 658 84-183 nfo.sit@rohde-schwarz.com

Phone +49 (22 03) 49-5 23 25 Fax +49 (22 03) 49-5 23 36 info.rssys@rohde-schwarz.com

> Phone +49 (431) 600 51-0 Fax +49 (431) 600 51-11 sales@gedis-online.de

Phone +49 (61 82) 800-0 Fax +49 (61 82) 800-100 info@hamen.de

#### **Locations Worldwide**

#### Please refer to our homepage: www.rohde-schwarz.com

- Sales Locations

- Service Locations

- National Websites

# **Customer Support**

### Technical support – where and when you need it

For quick, expert help with any Rohde & Schwarz equipment, contact one of our Customer Support Centers. A team of highly qualified engineers provides telephone support and will work with you to find a solution to your query on any aspect of the operation, programming or applications of Rohde & Schwarz equipment.

### **Up-to-date information and upgrades**

To keep your instrument up-to-date and to be informed about new application notes related to your instrument, please send an e-mail to the Customer Support Center stating your instrument and your wish. We will take care that you will get the right information.

USA & Canada Monday to Friday (except US public holidays)

8:00 AM - 8:00 PM Eastern Standard Time (EST)

Tel. from USA 888-test-rsa (888-837-8772) (opt 2)

From outside USA +1 410 910 7800 (opt 2)

Fax +1 410 910 7801

E-mail <u>CustomerSupport@rohde-schwarz.com</u>

East Asia Monday to Friday (except Singaporean public holidays)

8:30 AM - 6:00 PM Singapore Time (SGT)

Tel. +65 6 513 0488 Fax +65 6 846 1090

E-mail CustomerSupport@rohde-schwarz.com

Rest of the World Monday to Friday (except German public holidays)

08:00-17:00 Central European Time (CET)

Tel. from Europe +49 (0) 180 512 42 42\* From outside Europe+49 89 4129 13776 Fax +49 (0) 89 41 29 637 78

E-mail CustomerSupport@rohde-schwarz.com

\* 0.14 €/Min within the German fixed-line telephone network, varying prices for the mobile telephone network and in different countries.

| Gene  | 1-1                                                                                                                                     |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | User info                                                                                                                               | ormation                                                                                                                                                                                                                                                                                                       | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.2   | Reference                                                                                                                               | 1-1                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.3   | Explana                                                                                                                                 | tion of Symbols                                                                                                                                                                                                                                                                                                | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Softw | vare insta                                                                                                                              | allation                                                                                                                                                                                                                                                                                                       | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1   | General                                                                                                                                 |                                                                                                                                                                                                                                                                                                                | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

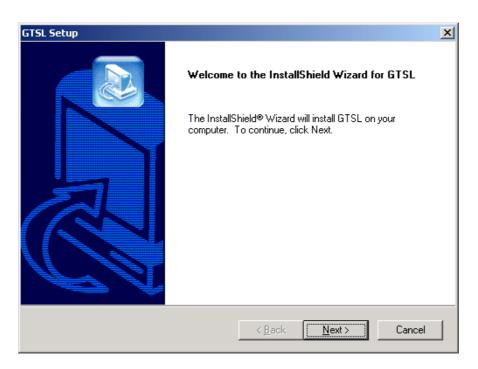

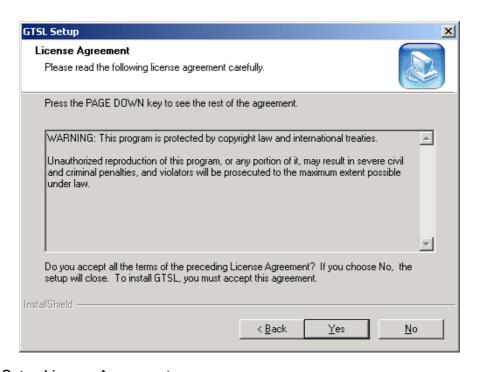

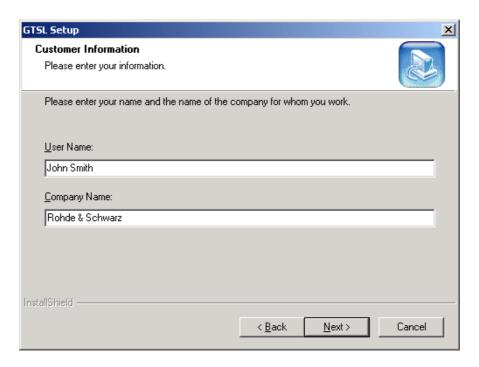

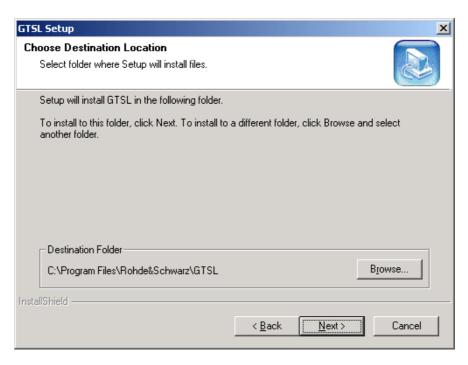

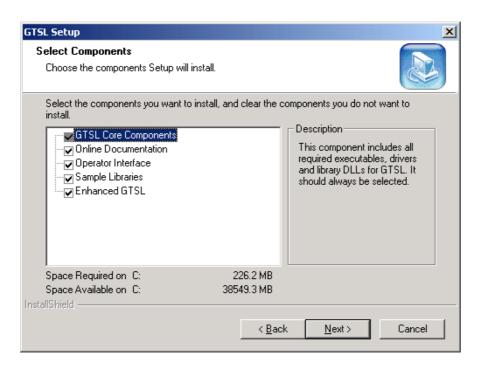

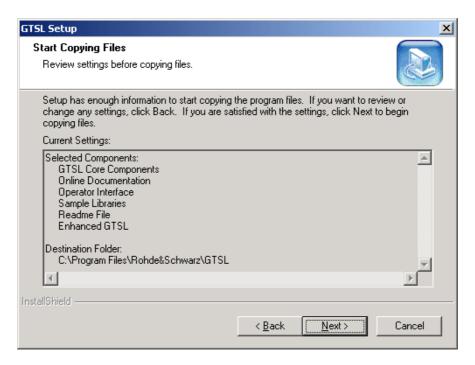

| 2.2   | Installati                                                                                                                              | ion                                                                                                                                                                                                                                                                                                            | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

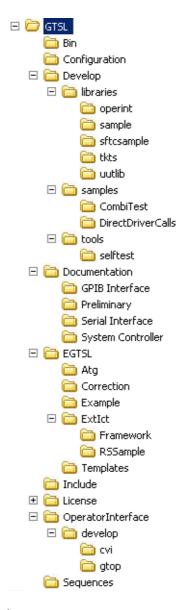

| 2.3   | File stru                                                                                                                               | cture                                                                                                                                                                                                                                                                                                          | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

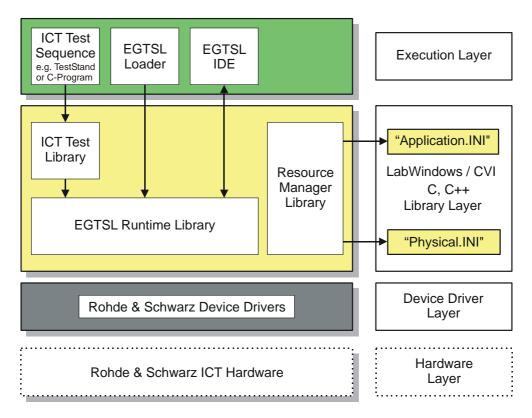

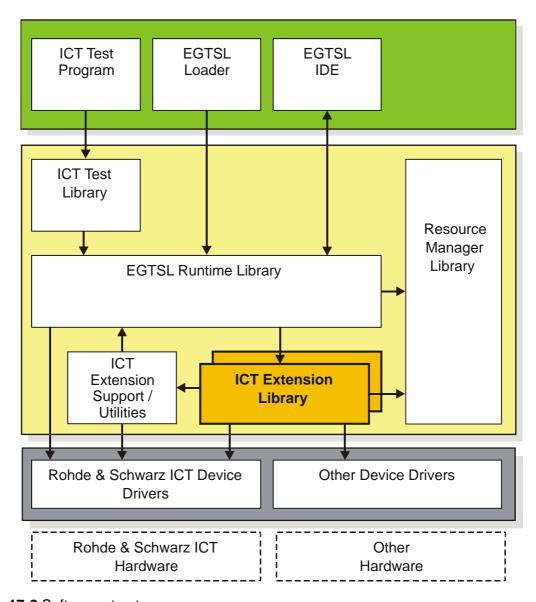

| Func  | tional de                                                                                                                               | escription                                                                                                                                                                                                                                                                                                     | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

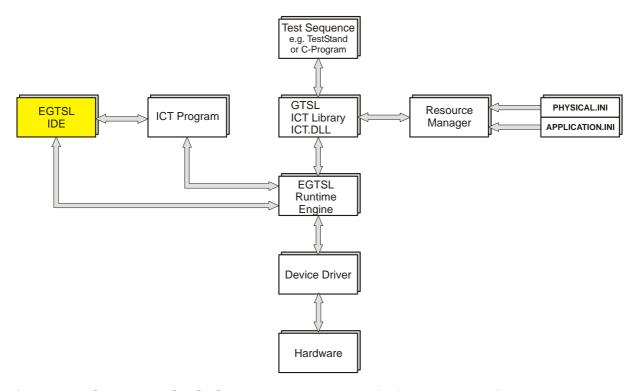

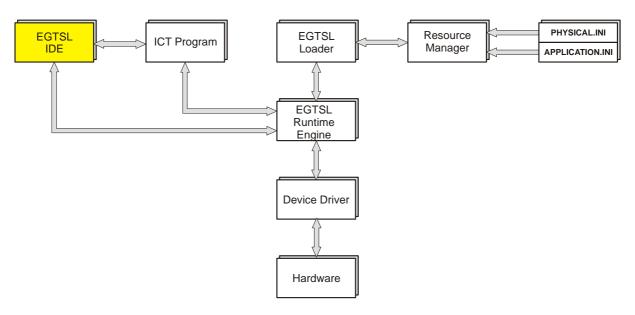

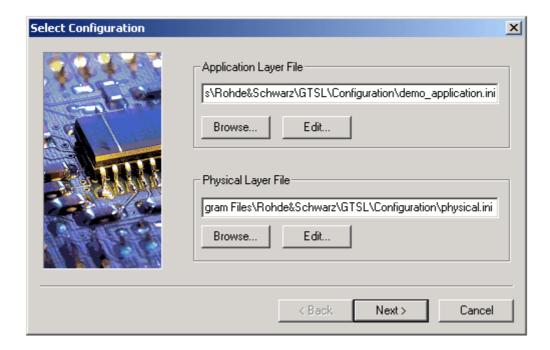

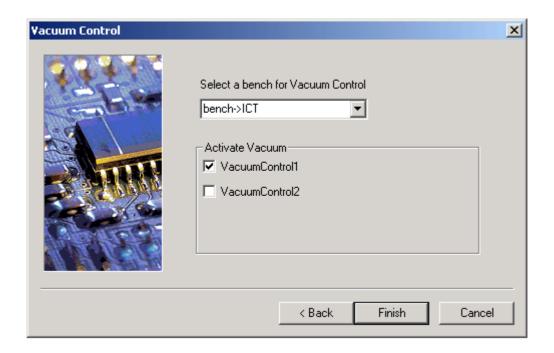

| 3.1   | General                                                                                                                                 |                                                                                                                                                                                                                                                                                                                | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2   | ICT test                                                                                                                                | library                                                                                                                                                                                                                                                                                                        | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 3.2.1                                                                                                                                   | General                                                                                                                                                                                                                                                                                                        | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 3.2.2                                                                                                                                   | Entries in PHYSICAL.INI                                                                                                                                                                                                                                                                                        | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 3.2.3                                                                                                                                   | Entries in APPLICATION.INI                                                                                                                                                                                                                                                                                     | 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 3.2.4                                                                                                                                   | Functions                                                                                                                                                                                                                                                                                                      | 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3   | R&S EG                                                                                                                                  | TSL Loader                                                                                                                                                                                                                                                                                                     | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

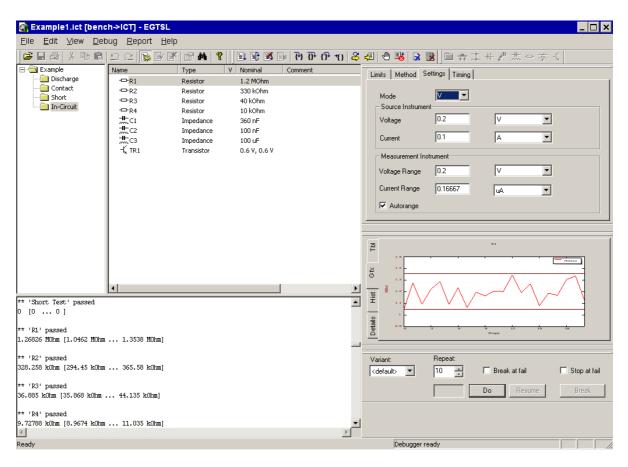

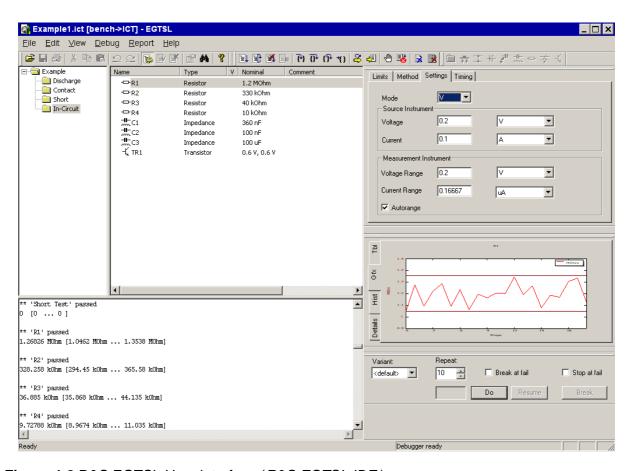

| 3.4   | R&S EG                                                                                                                                  | TSL user interface (R&S EGTSL IDE)                                                                                                                                                                                                                                                                             | 3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

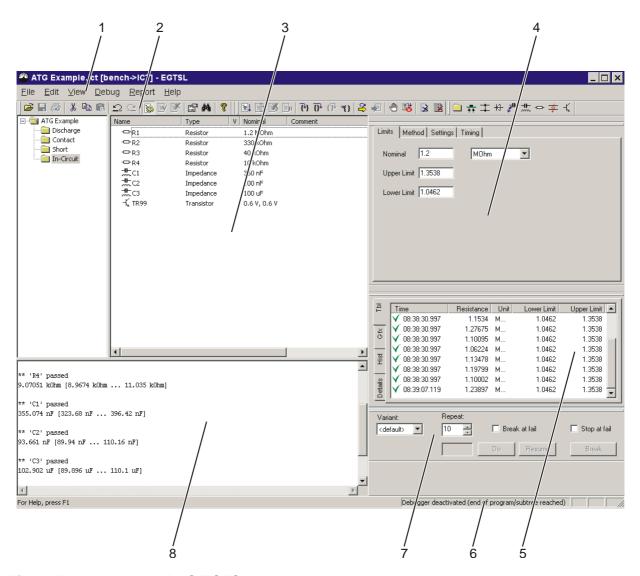

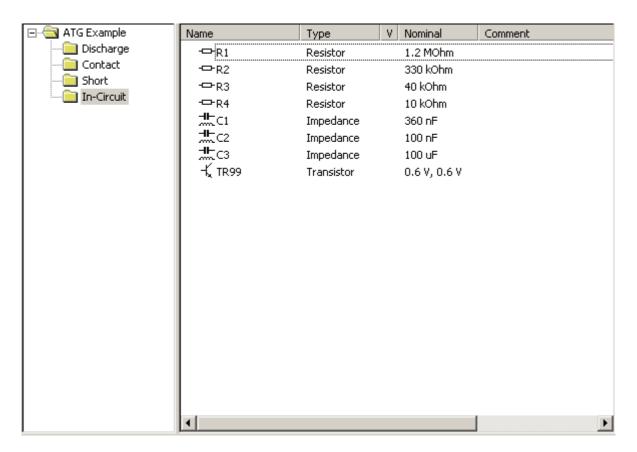

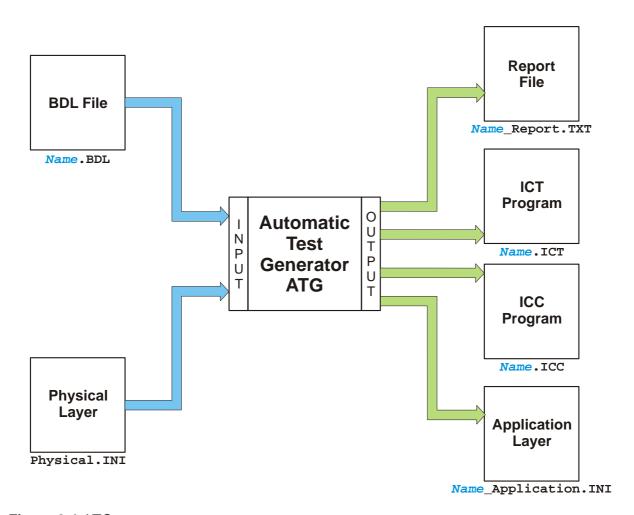

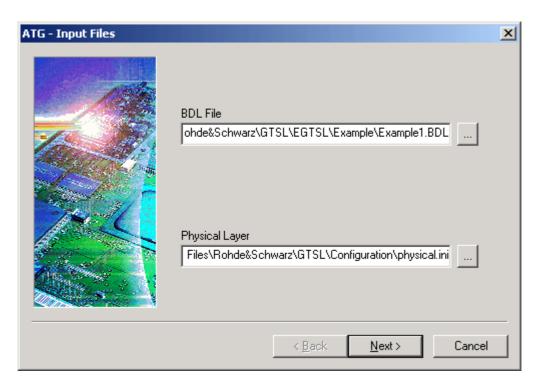

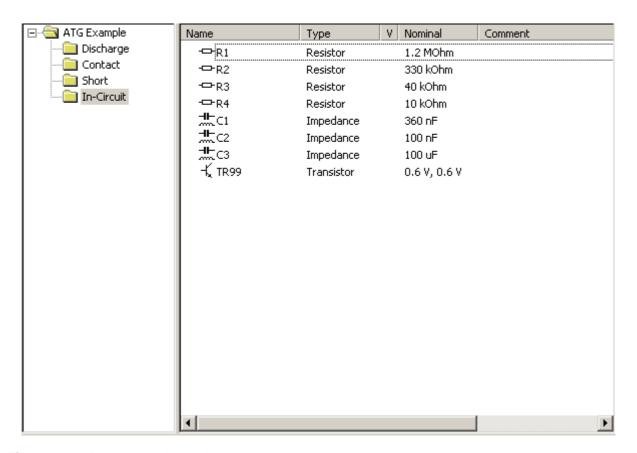

| 3.5   | Automat                                                                                                                                 | tic Test Generator ATG                                                                                                                                                                                                                                                                                         | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

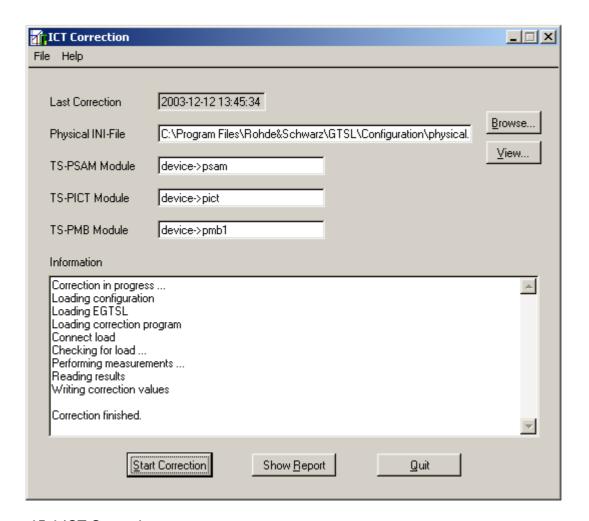

| 3.6   | ICT corre                                                                                                                               | ection data                                                                                                                                                                                                                                                                                                    | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

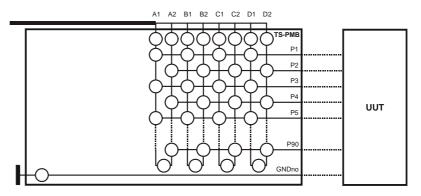

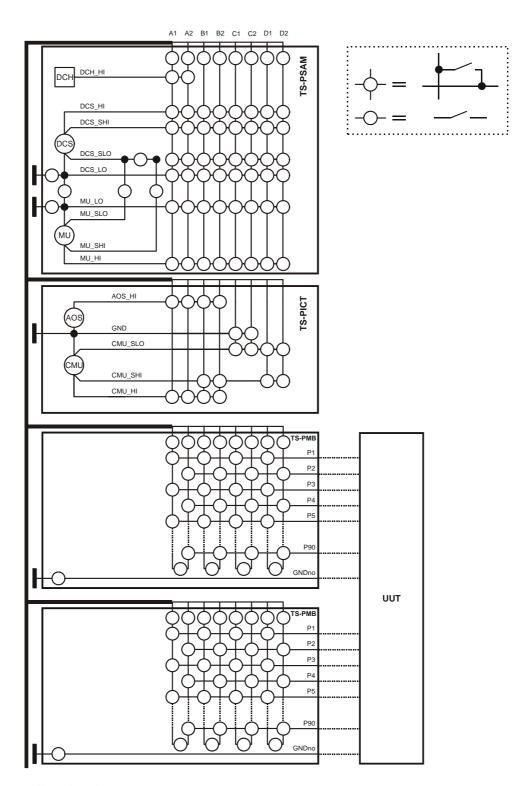

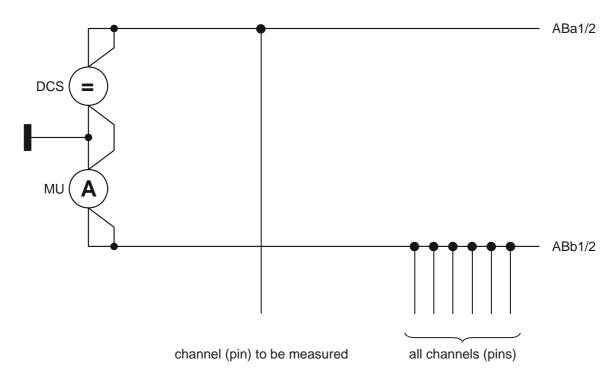

| 3.7   | Hardwar                                                                                                                                 | e for in-circuit test                                                                                                                                                                                                                                                                                          | 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Getti | 4-1                                                                                                                                     |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1   | General                                                                                                                                 |                                                                                                                                                                                                                                                                                                                | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

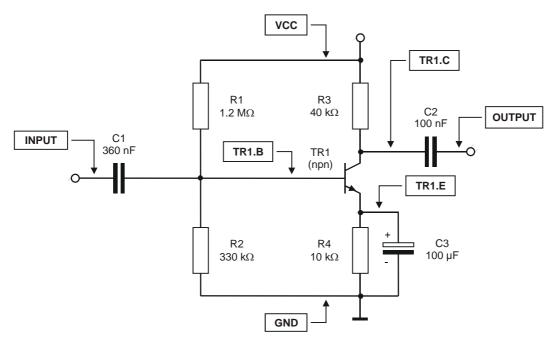

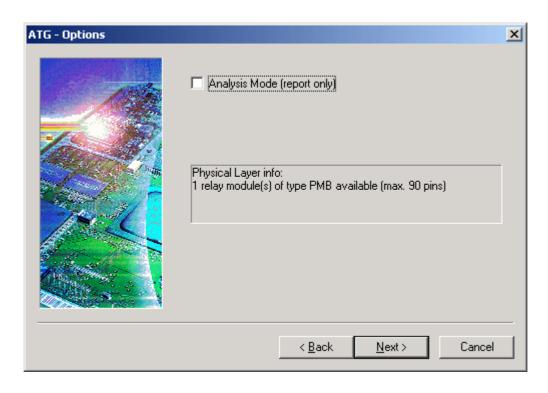

| 4.2   | Develop                                                                                                                                 | ment process for an in-circuit test                                                                                                                                                                                                                                                                            | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |